Project Overview

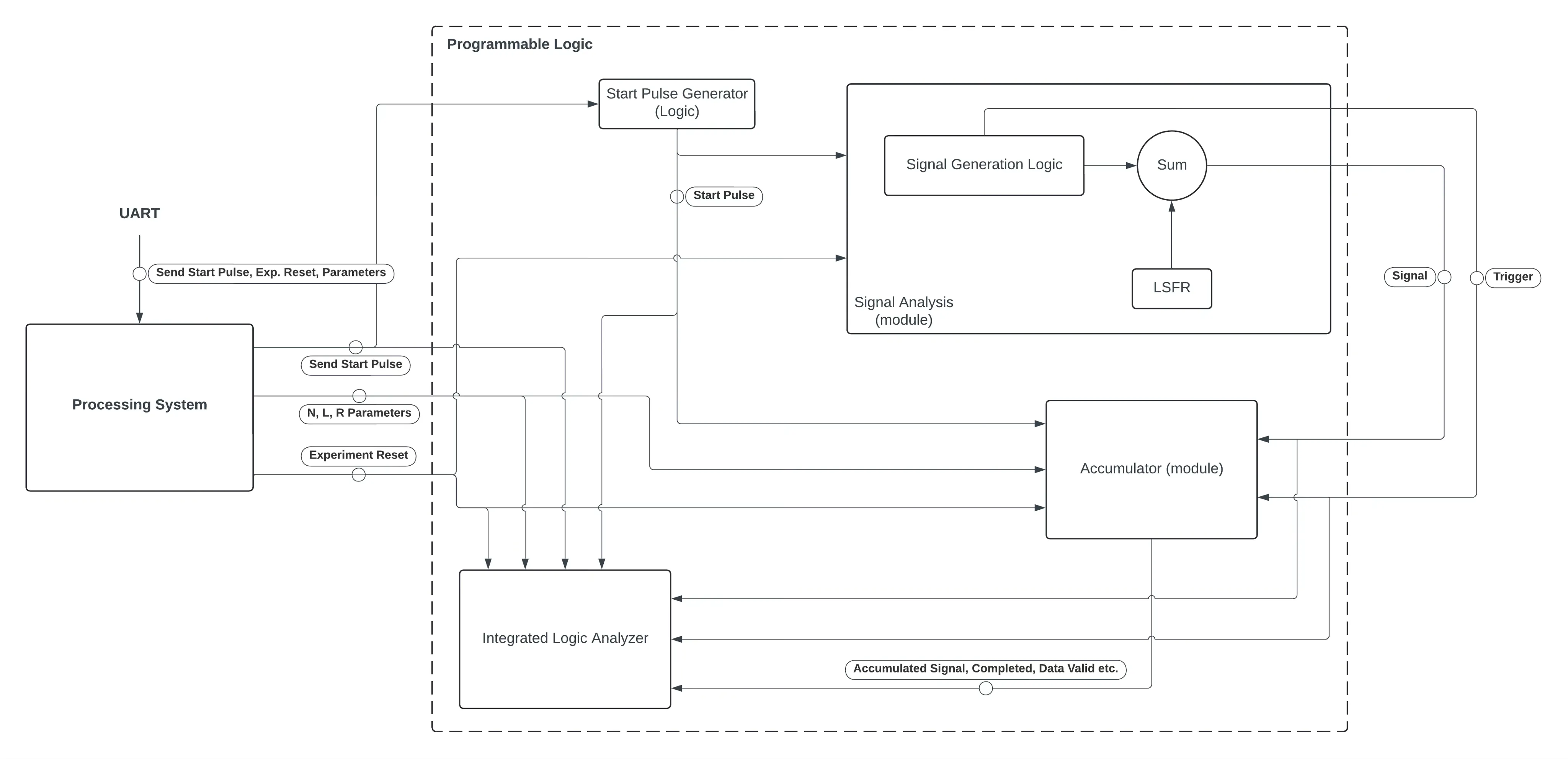

This project implements an FPGA-based prototype for quantum readout processing using a Red Pitaya platform. The system includes a segmented averaging module for processing noisy qubit readout signals, predefined Rabi and Ramsey experiment control logic, and a prototype qubit state discriminator based on digital downconversion (DDC) and thresholding.

Segmented averaging enables high-repetition signal averaging without storing full datasets, which is critical in memory-constrained FPGA environments. Experiment sequencing and configuration are controlled via a UART interface. Each module was verified independently using MATLAB simulations, on-hardware validation with Integrated Logic Analyzer (ILA), and external oscilloscope measurements. The system serves as a proof-of-concept toward a full quantum control and readout pipeline.

Segmented Averager Module

Quantum experiments often require averaging thousands of repeated measurement sequences to suppress noise and extract statistically meaningful observables. Direct storage of raw data is infeasible on FPGA platforms due to limited on-chip memory, while offloading data to external memory introduces latency and complexity. Under these conditions, a segmented averaging comes across as one of the strongest candidates for a hardware-based solution.

This system implements segmented averaging, where each measurement sequence is divided into fixed-length segments, and corresponding samples across repetitions are accumulated in a 36-bit signed fixed-point accumulator implemented in dual-port Block RAM.

Module Architecture

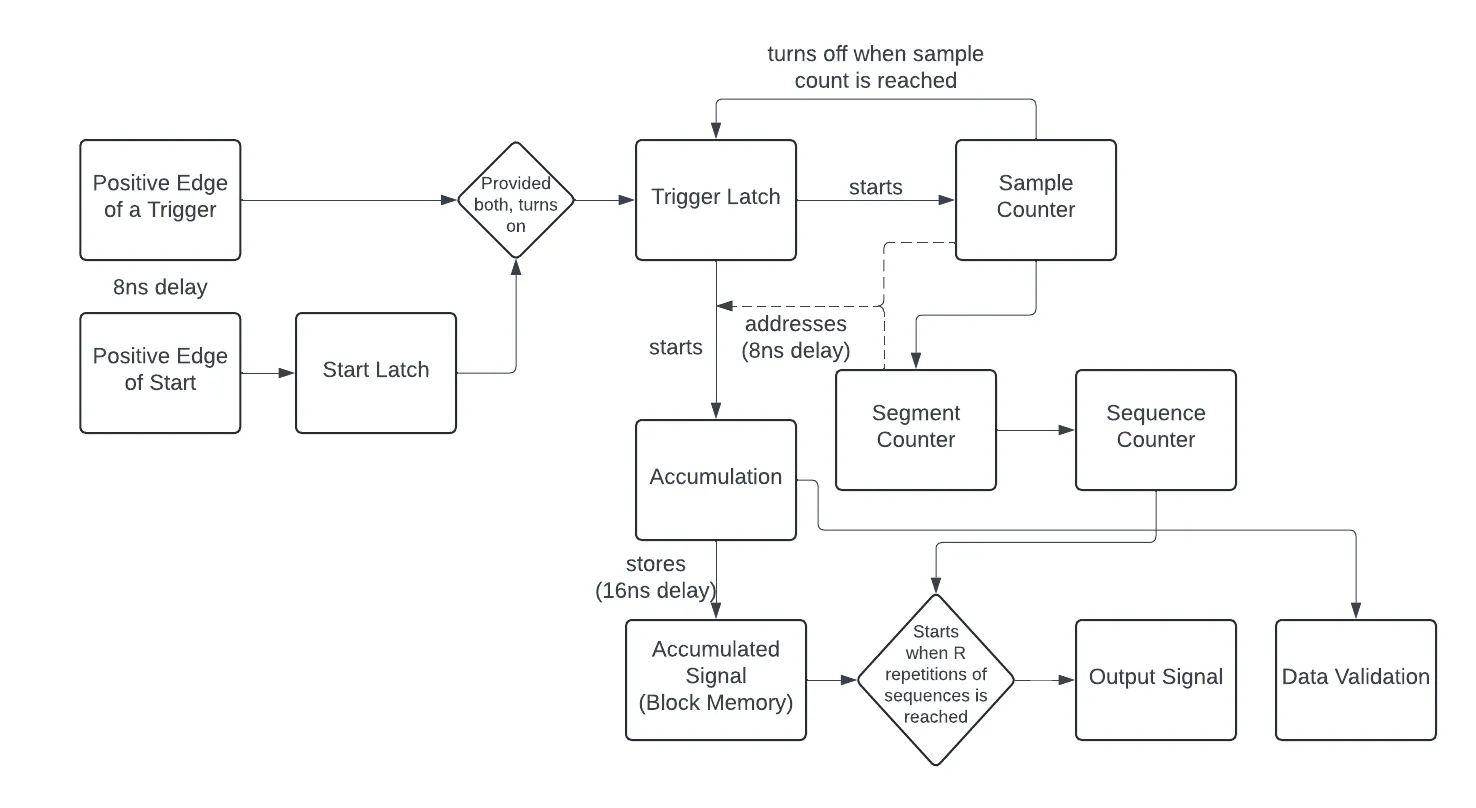

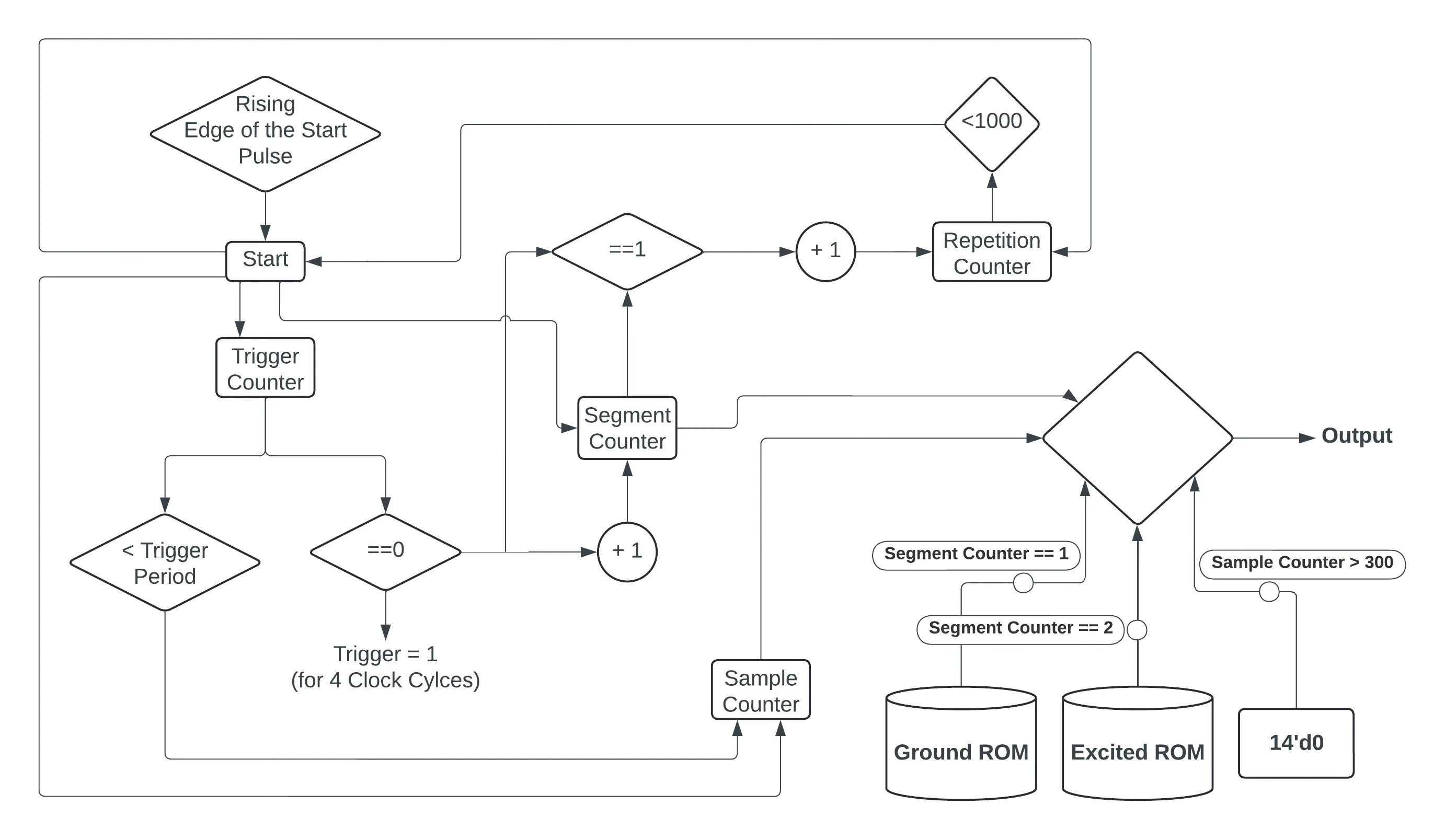

The module implements a set of internal triggers and counters to keep track of the accumulation progress. Trigger generation starts when the master start trigger is received. The received segments are held in Block RAM buffers and averaged once the accumulation is complete. The accumulation parameters are predefined by the user through a UART interface and the accumulation completes with the counter reaching the user-defined number of repetitions.

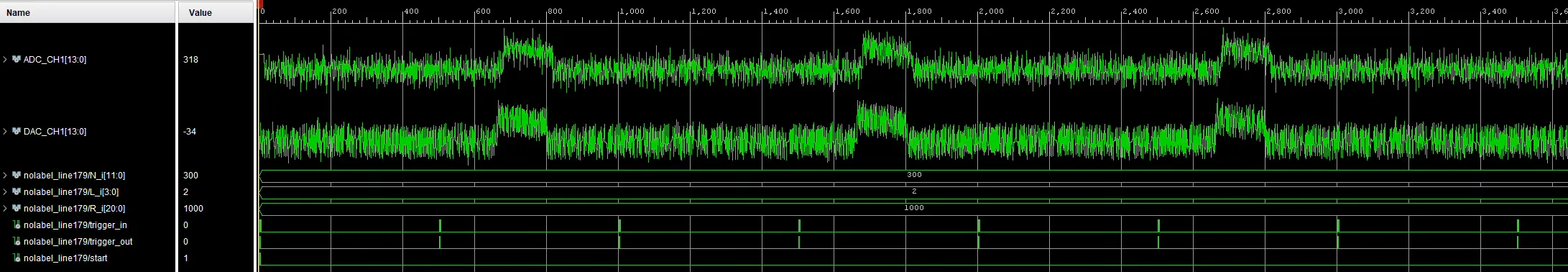

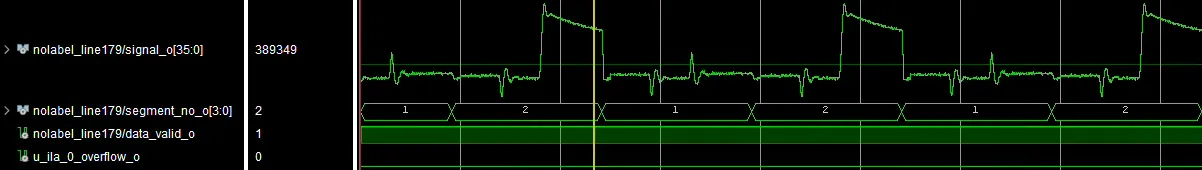

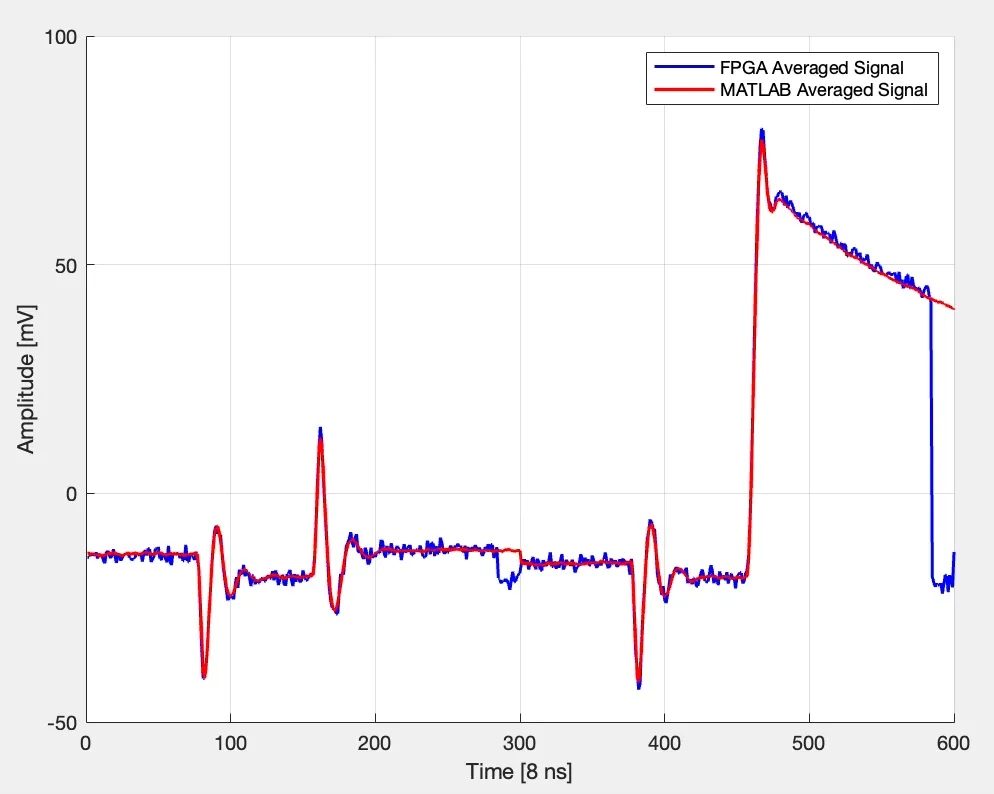

Functional Verification with Real Experiment data

For the functional verification of the module, two methods were used. First, different shapes of signals were generated using MATLAB and noise was added using an LFSR pseudo-random number generator. Second, real noisy experiment data was used to verify the module. The signals were then processed by the module and the results were compared to the expected values.

The resulting hardware implementation showed a 4.2% error rate compared to the MATLAB baseline. Simulations also showed a more positive 0.32% error rate. These results indicate that the system operates as expected and can be implemented in front of a state discriminator.

Performance Metrics and Resource Utilization

Resource utilization for the segmented averager module shows a low utilization of the available resources, allowing implementation in a larger system.

| Resource | Utilization | Available | Utilization % |

|---|---|---|---|

| LUT | 498 | 17600 | 2.83 |

| FF | 243 | 35200 | 0.69 |

| BRAM | 20 | 60 | 33.33 |

| DSP | 1 | 80 | 1.25 |

| IO | 98 | 100 | 98 |

| BUFG | 1 | 32 | 3.13 |

With the routing performed, design synthesized at 125 MHz with positive 1.711ns WNS timing margin. While this clock is insufficient for an actual quantum experiment, it allowed a proof-of-concept implementation which may be further scaled up to a fully operational system.

Quantum Control Module (Predefined Rabi and Ramsey Experiments)

The Quantum Control Module has been implemented but due to a lack of prior documentation, body will be added later. You may check the GitHub repository for project files.

State Discriminator Module

The State Discriminator Module has been implemented but due to a lack of prior documentation, body will be added later. You may check the GitHub repository for project files.